Embedded World 2013 — что новенького?

на прошлой неделе нам посчастливилось побывать на международной выставке Embedded World 2013, которая уже не первый год проводится в Нюрнберге (Германия). Эта выставка посвящена встраиваемой электронике (embedded). Я хочу немного рассказать о своих впечатлениях :)

на прошлой неделе нам посчастливилось побывать на международной выставке Embedded World 2013, которая уже не первый год проводится в Нюрнберге (Германия). Эта выставка посвящена встраиваемой электронике (embedded). Я хочу немного рассказать о своих впечатлениях :)

выставка занимает более 5 павильонов и проводится в Nurnberg Messe

мы приехали туда втроём.

Артём Двинин(artem) и Павел Курочкин(pk)

и Александр Степанов (stepanov)

на выставке было выставлено множество плат с процессорами, периферийными компонентами, разными разъёмами и прочими embedded-примочками.

я для себя отметил следующий тренд: это SoC-решения. SoC — system on chip, система на одном кристалле.

как минимум четверо крупных участников представили свои новые чипы, в которых процессор объединён с программируемой логикой в одном чипе. Xilinx представил Zync, Altera — V поколение, Cypress — PSoC,

Actel (он же Microsemi) — SmartFusion.

Обо всём по порядку.

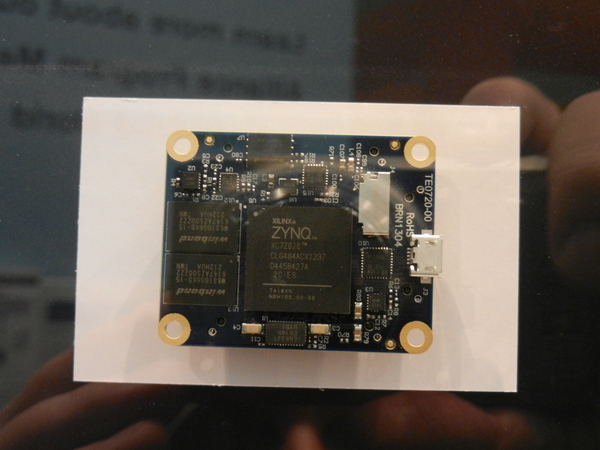

Xilinx Zync

Чипы этой серии уже производятся и доступны для широкого круга. цена за чип — не более 50 долларов при партии 1000 штук (модель уточню чуть позже). то есть довольно-таки неплохо, учитывая, что это не просто FPGA, но и ещё и довольно мощный процессор.

Что имеем: двухядерный процессор Cortex A9 с частотой 0.8-1 ГГц + FPGA различной ёмкости. тех. процесс — 28 нм. на этот Cortex устанавливается linux, имеется IDE для разработки FPGA, ну и т.п.

что порадовало? огромное количество всевозможных готовых плат на базе Zync. Их предлагают Trenz Electronic, ITR, PLDA.

учитывая тот факт, что микросхемы уже вовсю производятся, можно начинать разрабатывать на базе Zync и закладывать его в новые продукты.

Altera Family V

похоже, Altera пока проигрывает позиции своему основному конкуренту — Xilinx. пятое семейство имеет практически такую же начинку, что и Zync, но пока представлены только инженерные образцы. массовый выпуск планируется начать в мае. однако, уже готовы и платы на базе этих инженерных образцов.

например, SoCrates by EBV Electronik (www.ebv.com) — очень интересная платка

что порадовало? был продемострирован отладчик (которого, по рассказам представителей Altera, нет у Xilinx), позволяющий отлаживать ARM+FPGA синхронно. называется он DS-5 и основная его «фишка» в том, что работу прошивки FPGA можно сопоставить с кодом, выполняемым в Cortex’е, даже по времени. это хорошо видно из описания и скриншота.

событие, генерируемое из FPGA, останавливает процессор в точке, соответствующей данному моменту времени. дальше можно следовать по шагам, просматривать регистры и т.п.

Actel (Microsemi) Smart Fusion

это тоже процессор + FPGA, только процессор чуть послабже, а именно — Cortex-M3. зато какой там FPGA!

в этом устройстве больше всего порадовала его цена — около 300 долларов за чип (не помню точно, за какой, но количество LE там около 50000) :)

Высокая цена обусловлена устройством FPGA — состояние каждой ячейки (LE) сохраняется во флеш и при включении инициализируется из этой флешки. включение происходит с молниеносной скоростью и не требует высокого тока включения (я правильно выражаюсь?).

данное предложение актуально для военных целей, авионики.

как устроен этот flash FPGA в подробностях, я пока не нашёл :(

Cypress PSoC

помните те времена, когда в микроконтроллере было фиксированное количество i2c, spi, etc.. контроллеров и они были жёстко привязаны к определённым ножкам? так вот можете про них забыть. это — прошлый век :)

PSoC — это конструктор, где кирпичиками являются так называемые UDB (universal device block). для чипа, установленного на плате и подключенного к какой-то перефирии разработчик создаёт проект, в который добавляет нужные контроллеры из библиотеки компонентов. каждому добавленному компоненту назначаются ножки и базовый адрес (причём на выставке мне говорили, что идентификатором каждого компонента является строка, но я не верю ;) — проверю ). Один контроллер может занимать один или несколько UDB-блоков.

список компонентов, доступных в библиотеке, есть на сайте компании. важно отметить, что поведение любого компонента можно изменить: берём Verilog в руки и правим или создаём свой!

а! чуть не забыл про ложку дёгтя: этот самый PSoC creator работает только под windows :)

SATA + NAND

очень понравился чип, который интегрирует в себе SATA-контроллер и NAND-флеш. при этом чип имеет одинаковый footprint независимо от объёма и объём достигает 64 ГБ. встроенный контроллер берёт на себя заботы о bad-блоках и прочих орг. вопросах, а в системе этот чип виден как обычный sata-диск.

фото

Средства измерения

порадовал tektronix демонстрацией своего multi-domain осциллографа (может быть для кого-то это обыденный девайс, но для меня — новость :) ) он умеет записывать аналоговые, цифровые и радиочастотные процессы, происходящие, естественно, параллельно. 4 канала на аналог/цифру и 1 RF.

я на этот стенд зашёл просто из любопытства и мне показали маленькое шоу на тестовой плате, управляющей радиочастотой. управление производилось по SPI. чип, управляемый по SPI-шине, рулит напряжением, а оно уже частотой. и на осциллографе можно увидеть все эти процессы: декодированные SPI-посылки, радиочастотный спектр, уровень аналогового сигнала. и, главное, всё это можно записать для последующего анализа. и триггеры можно устанавливать по всем каналам! меня впечатлило.

а цена у этого девайса немалая =)

см. сюда

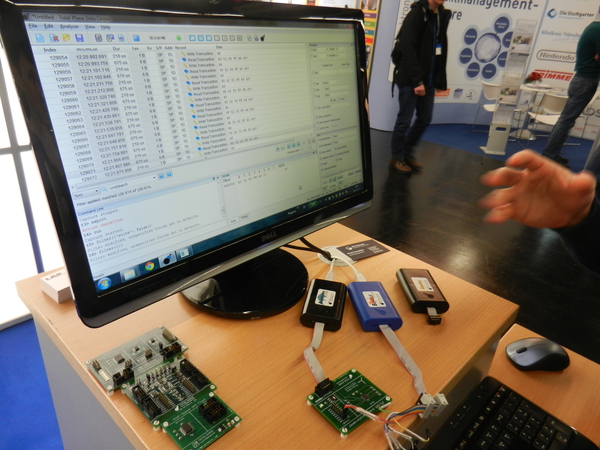

мониторинг i2c

также был представлен инструмент для мониторинга i2c-шины. небольшая USB-коробочка подключается к i2c и записывает всё, что происходит на шине. далее в окне программы можно увидеть всё — от коллизий, возникших на шине, до протокола обмена между устройствами. предусмотрен поиск и прочие удобные «крутилки». очень удобная вещь! и цена довольно гуманная — 300 долларов (плата + софт), особенно если учесть сколько времени мы потратили на отладку i2c-шины :) аналогичное решение предлагается и для SPI-шины.

Redundant switch

интересного «монстра» показала одна финская компания (http://www.flexibilis.com)

как бы вы думали, что это? :)

это система с резервированием каналов. образует гигабитную оптическую сеть и обеспечивает устойчивость при пропадании одного или нескольких линков.

подробнее можно почитать на родном сайте. там и схема есть, и объяснение.

заключение

было очень интересно. практически никакой попсы (в последнее время набили оскомину павильоны, забитые стендами операторов связи), только платки и железяки. приятно чувствовать себя в такой среде, как рыба в воде :)

я для себя взял многие идеи на вооружение и буду применять их в новых разработках. и, честно говоря, хотелось бы в следующем году выставиться на такой выставке. посмотрим, может быть и получится ;)

ну и без баварского пива не обошлось, конечно же. это было приятным продолжением нашего путешествия.

и в заключение скажу, что мог я, конечно, что-то не так записать или понять. поэтому проверяйте

информацию на официальных сайтах, пожалуйста.

вот пара статей, из которых можно понять принцип работы flash based fpga:

http://www.1-core.com/library/digital/fpga-architecture/

http://www.actel.com/products/milaero/rtpa3/default.aspx

грубо говоря, состояние каждого транзистора сохраняется при выключении питания.

таким образом, при включении fpga не требует инициализации.

и такие fpga устойчивы к радиации. чудо техники, короче :)

сам написал, сам и прокомментирую ;)

только что обнаружил на сайте поставщиков микросхем такое вот объявление

цитирую «На текущий момент доступны для отгрузки образцы Систем-на-Кристалле с интегрированной ПЛИС серии Cyclone V (5CSXA6), со 110 тыс. логических элементов (LE)»